Proiectul AVESIC (cod proiect: PN-III-P2-2.1-PTE-2021-0460) este finanțat de Unitatea Executivă pentru Finanțarea Învățământului Superior, a Cercetării, Dezvoltării și Inovării (UEFISCDI) prin programul Transfer la operatorul economic (PTE) în cadrul competiției PN-III-P2-2.1-PTE-2021, cu numărul de contract 90PTE/2022. Proiectul a fost implementat între iunie 2022 și iulie 2024.

Echipa de proiect:

|

|

Problemele de verificare a circuitelor integrate sunt caracterizate de un număr de condiții de operare (de obicei până la 10) și un număr foarte variat de caracteristici electrice urmărite (răspunsuri) pentru care trebuie găsite cazurile cele mai nefavorabile (worst cases). În plus, trebuie luată în considerare și variația procesului de fabricație. În industria de semiconductori, numărul de simulări e limitat de constrângeri legate de considerente economice și de presiunea de lansare cât mai repede pe piață. Din aceste motive, simulările trebuie executate într-un număr mic de iterații (ideal mai puțin de 10). Un lot de simulări executat in paralel poate dura până la 24 de ore și întregul proces de verificare trebuie să dureze cel mult o săptămână.

În proiectul AVESIC noi avem ca obiectiv aducerea la Nivel de Maturitate Tehnologică 6 (TRL6) a unui algoritm de verificare adaptivă cu scopul de a reduce numărul de simulări necesar față de metoda clasică de verificare, fără a pierde din acoperire. Algoritmul combină o etapă de planificare de experimente fixă care oferă o acoperire optimă a spațiului parametrilor de intrare, urmată de o etapa de planificare adaptivă, în care simulările vor fi adaptate nevoilor de verificare pentru fiecare răspuns, căutând cazul cel mai defavorabil pentru fiecare.

Pentru a atinge TRL6, acest algoritm va fi implementat într-o unealtă software ce va avea capacitatea de a controla o gamă largă de condiții de operare și parametri de proces. Unealta va fi capabilă să trateze circuite de complexități mai ridicate prin paralelizarea procesului de verificare și să trateze și excepții de la abordarea uzuală a procesului de verificare. Unealta va fi dotată cu o interfață grafică interactivă, și elemente de raportare automată care să faciliteze adoptarea de către inginerii de verificare. Pentru a maximiza beneficiul algoritmului, unealta va fi integrată în procesul de dezvoltare al Infineon, astfel încât toți inginerii să beneficieze de ea.

Scopul proiectului constă în îmbunătățirea unei tehnologii de verificare adaptivă asistată de inteligență artificială (IA) de la stadiul de unealta software programabilă validată in condiții restrânse (TRL4) la stadiul de prototip validat în condiții reale de utilizare (TRL6). Acest lucru presupune un efort de cercetare care să conducă la îmbunătățirea algoritmilor pentru a putea fi dezvoltați și integrați în aplicațiile software care sunt folosite în fluxul de verificare din Infineon.

În urma unor colaborări anterioare, membrii proiectului au dezvoltat o metodologie de verificare bazata pe IA care a fost testată cu succes pe un număr limitat de circuite de complexitate relativ mică. Au fost constatate îmbunătățiri semnificative în ceea ce privește acoperirea spațiului definit de condițiile de operare ce definesc funcționarea circuitelor precum și eficiența în ceea ce privește timpul total de verificare comparativ cu metodele clasice utilizate în mod curent. Totuși, acești algoritmi necesită anumite îmbunătățiri în ceea ce privește capacitatea lor de a fi folosiți în contexte mult mai generale și de a putea înlocui cu succes metodologiile actuale. Printre aceste îmbunătățiri se pot enumera creșterea capacității algoritmilor de a putea face față unei complexități mai mari a procesului de verificare, caracterizat de un set mai mare de condiții de operare si de a controla și investiga efectul parametrilor de proces tehnologic (variația de proces) asupra caracteristicilor electrice (răspunsurilor) în mod simultan. De asemenea, metodologia de verificare va trebui sa poată fi aplicată de utilizatori (ingineri de verificare) care, deși au cunoștințe inginerești solide, să nu necesite să dețină o expertiză solidă în domeniul IA.

Prima etapă a proiectului AVESIC a avut trei obiective principale care au fost realizate în proporție de 100%:

Activitățile realizate în etapa 1/2022 au fost următoarele:

A II-a etapă a proiectului AVESIC a avut obiective principale care au fost realizate în proporție de 100%:

Activitățile realizate în etapa 2/2023 au fost următoarele:

A III-a etapă a proiectului AVESIC a avut obiective principale care au fost realizate în proporție de 100%:

Activitățile realizate în etapa 3/2024 au fost următoarele:

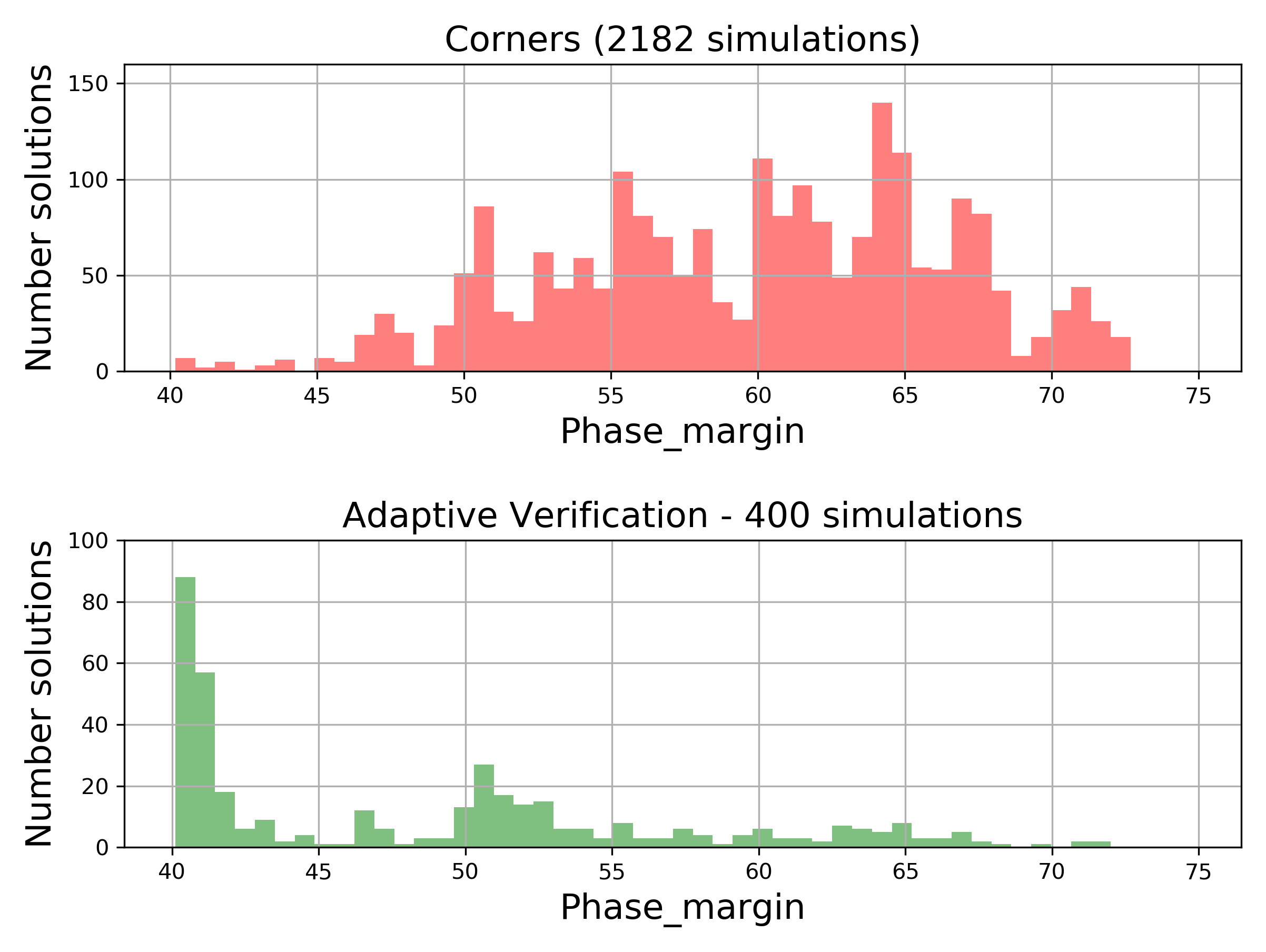

Verificarea unui circuit folosind metoda clasică în colțuri (2182 simulări), prezentată în figura de mai jos (graficul de sus) cheltuie majoritatea simulărilor departe de zona țintă (în acest caz valori mici ale marginii de fază).

Verificarea cu algoritmul adaptiv prezentată în graficul de jos folosește o fracțiune importantă ale celor 400 de simulări pentru a explora zona țintă.

Algoritmul adaptiv reduce de 5 ori numărul de simulări necesare pentru aceeași acoperire.

Tehnologia de verificare adaptivă a fost adusă la TRL5 în cursul Etapei 2. Robustețea verificării a fost îmbunătățită: algoritmul actual poate gestiona oricâte condiții de operare (CO), iar nivelul de verificare adaptivă al tehnologiei a fost crescut pentru a permite verificarea tuturor răspunsurilor în același timp. Tehnologia de verificare asistată de IA produce rezultate bune pentru o serie de circuite sintetice proiectate special pentru acest scop, cât și pe circuite reale.

Algoritmul a fost testat extensiv cu un circuit sintetic cu 6 OC, 1 PC și 25 de răspunsuri. Principalul avantaj al utilizării acestui circuit este că, datorită naturii analitice a răspunsurilor, acestea sunt foarte rapid de calculat și au un minim și un maxim cunoscut. Astfel, putem evalua mai bine performanța algoritmului.

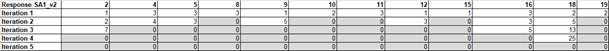

Nivelul de automatizare trebuie a fost îmbunătățit semnificativ: tehnologia prototip a fost încorporată într-o unealtă software cu o interfață grafică de utilizare care permite inginerului de verificare să conecteze ușor simulările cu algoritmii de IA. Unealta de verificare adaptivă a fost testată în mediul relevant (în mediul de dezvoltare) de către un grup de ingineri de verificare, care au ghidat și verificat că îndeplinește performanțele vizate. Au fost efectuate peste 1200 de teste cu unealta integrată. Dintre acestea, 300 de teste s-au terminat cu succes, 600 s-au terminat cu eroare, iar 300 au fost terminate prematur.

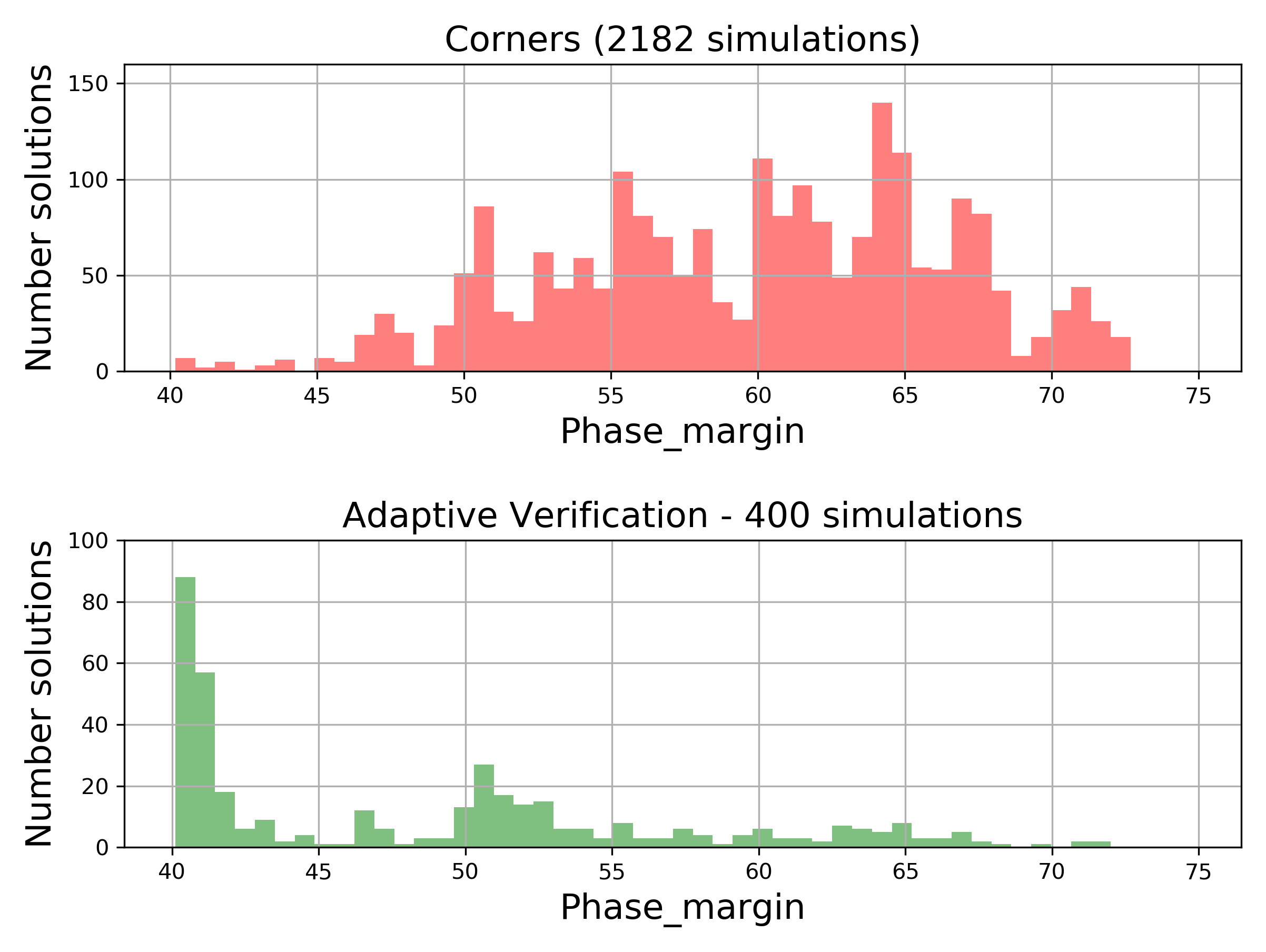

Algoritmul de verificare adaptivă a circuitelor analogice a fost îmbunătățit la varianta descrisă schematic în figura de mai sus. Acoperirea inițială a spațiului de intrare este foarte importantă, după cum s-a demonstrat în pachetele de lucru anterioare. Pentru a optimiza acoperirea a fost utilizată o combinație de Orthogonal Arrays + Latin Hypercube Sampling, pentru un buget de 100 de simulări. Orthogonal arrays utilizează valorile colțurile și centrele intervalelor de variație întrucât inginerii folosesc deja valorile nominale pentru condițiile de intrare. Din experiență aceste colțuri ar putea oferi informații valoroase. A fost introdusă o metrică de risc, probabilitatea de a încălca specificația, sau PVS (Probability to Violate the Specification). Aceasta este calculată la fiecare iterație, pentru fiecare răspuns, limitând efortul de calcul prin grupare K-means. A fost introdusă alocarea inegală a bugetului, la fiecare iterație. Se utilizează metrica PVS pentru a aloca simulările rămase la răspunsurile cu PVS mai mare sau cu cea mai mare schimbare de a încălca specificația în iterațiile următoare.

Algoritmul îmbunătățit a fost evaluat pe un circuit sintetic cu extreme cunoscute în două experimente:

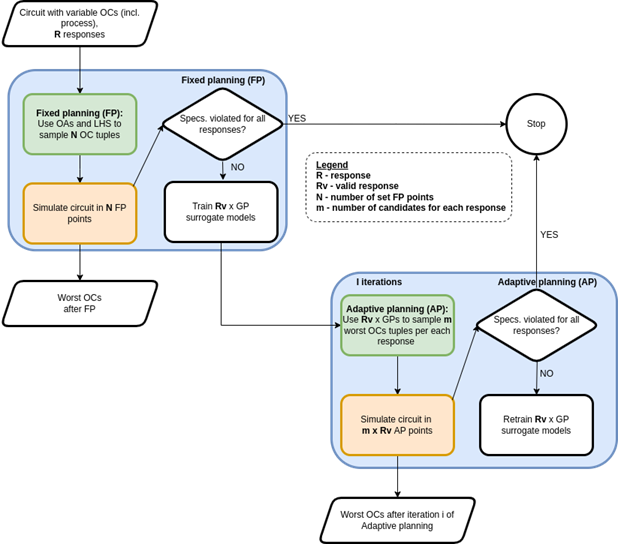

Pentru primul caz, dacă specificațiile nu pot fi încălcate, algoritmul funcționează într-un mod foarte asemănător cu algoritmul anterior. Metrica PVS este destul de fiabilă, după cum se poate observa în figura de mai sus. Pentru unele răspunsuri (7, 14 și 19), în care specificațiile sunt foarte aproape de minimul adevărat, valorile pentru PVS sunt încă ridicate și, cel mai probabil, mai au nevoie de câteva iterații pentru a obține o tendință descendentă, dezirabilă. Dar pentru restul răspunsurilor, valorile PVS scad pe măsură ce avansăm cu iterațiile. Algoritmul ajunge la valori minime reale pentru toate cele 25 de răspunsuri după 9 iterații. Am observat o valoare a RVE (per-response absolute verification error) maximă foarte bună de 0,01%, atinsă după 6 iterații. În ceea ce privește alocarea bugetului, a fost alocată o singuă simulare pentru fiecare răspuns. Este așa cum era de așteptat, deoarece nu a fost încălcată nicio specificație și nu avem simulări suplimentare de alocat.

În cazul în care specificațiile pot fi încălcate, putem observa algoritmul de buget inegal în funcțiune, în figura de mai sus. Algoritmul începe să aloce mai multe simulări pentru răspunsurile cu PVS ridicat. Criteriul de oprire este, de asemenea, îndeplinit, la iterația 4, când toate răspunsurile au fost încălcate. Ca atare, nu sunt utilizate toate iterațiile, în comparație cu algoritmul anterior, iar algoritmul se oprește.

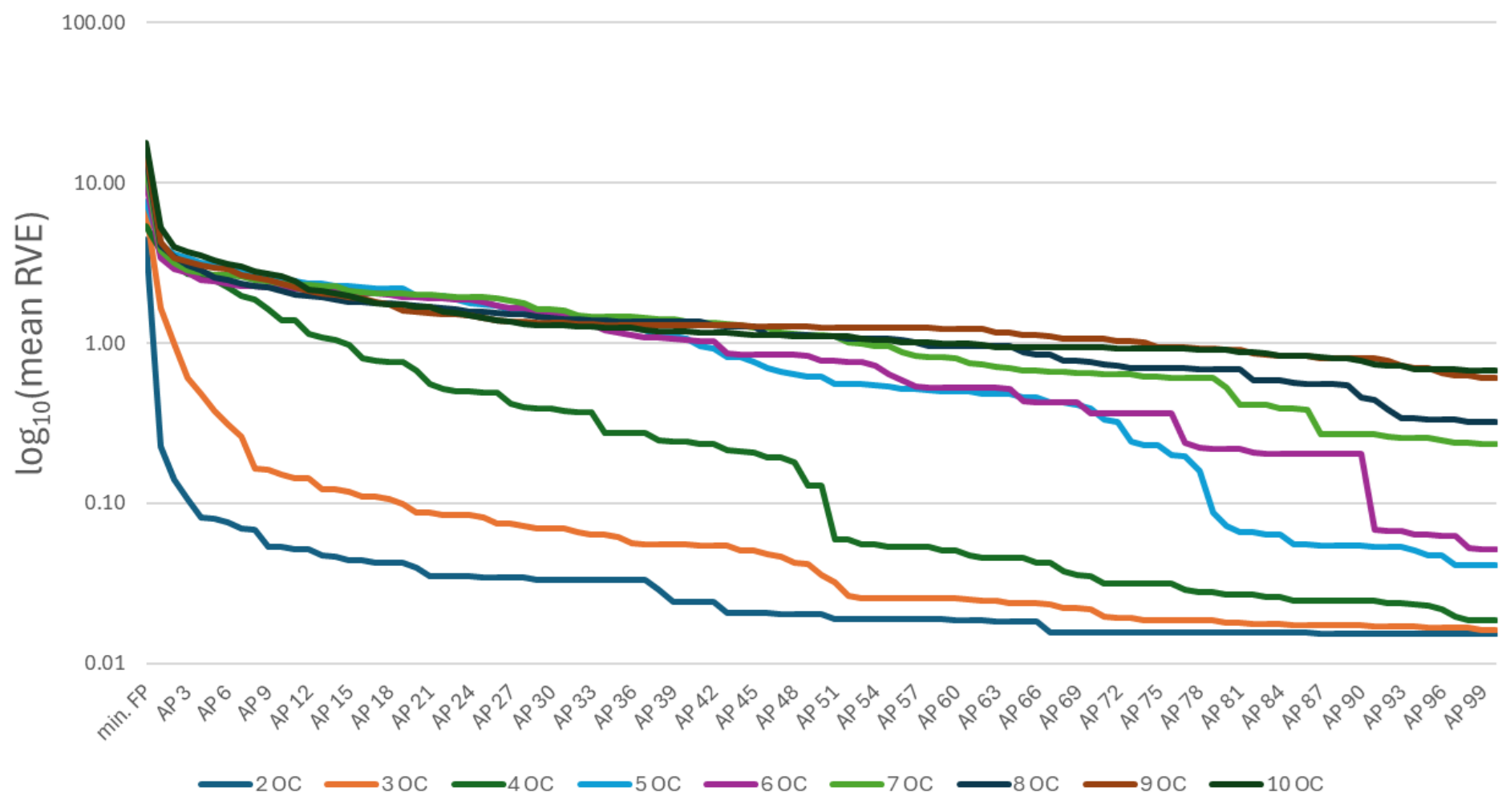

Pentru evaluarea extensivă a algoritmului adaptiv am dezvoltat un set de circuite sintetice având între 2 și 10 condiții de operare, la care cunoaștem minimele și maximele reale ale funcțiilor de răspuns și astfel putem evalua corect performanța algoritmului nostru prin compararea celor mai rele cazuri găsite de algoritm cu aceste valori. În acest scop, folosim eroarea de valoare relativă (relative value error, RVE), care reprezintă diferența dintre minimul găsit de algoritmul nostru și minimul real al funcției de răspuns în raport cu intervalul de răspuns. O valoare RVE de 0% indică faptul că algoritmul a găsit adevărata valoare minimă a unei funcții, dar, pentru a vedea cât de bine se comportă algoritmul cu diferitele funcții de referință, vom evalua cât timp este necesar, în termeni de număr de iterații, pentru a atinge valori RVE sub 2%.

Folosind setul de circuite sintetice, a fost efectuat un experiment extins care a implicat 100 de circuite sintetice create anterior pentru fiecare număr de OC, variind de la 3 la 10 OC. Fiecare experiment a fost replicat cu 5 random seeds diferite pentru a asigura robustețea și fiabilitatea rezultatelor. Rezultatul acestor experimente a indicat că liniile directoare propuse sunt consecvente în ciuda variațiilor introduse de diferite random seeds, subliniind fiabilitatea acestora.

Algoritmul de verificare se comportă foarte bine în cazul circuitelor cu două până la șapte OC de intrare, reușind să găsească valori apropiate de minimul adevărat pentru până la 70% din circuite în mai puțin de 10 iterații AP. Pentru circuite cu mai mult de 7 OC numărul necesar de iterații crește. În ceea ce privește iterațiile AP, cu excepția seturilor cu un număr mic de OC de intrare, este nevoie de o medie de 10-20 de iterații pentru a atinge un RVE sub 2%.

Figura de mai sus prezintă valoarea medie RVE pentru nouă seturi de evaluare ale diferitelor OC, fiecare cu 100 circuite. Valoarea medie RVE pentru un set de evaluare (de exemplu, 3 OC) reprezintă valoarea medie RVE pentru toate cele 100 de circuite ale setului de evaluare respectiv, calculată la fiecare iterație, inclusiv etapa FP. Graficul este prezentat în formă logaritmică. Pornind de la etapa FP și trecând la iterații mai mari, putem observa scăderea valorilor medii RVE în toate seturile de evaluare. În plus, se pot observa tendințe mai abrupte pentru seturile cu un număr mic de OC (de exemplu, 2, 3 și 4), în comparație cu un comportament mai lin pentru cele de un ordin OC mai mare.

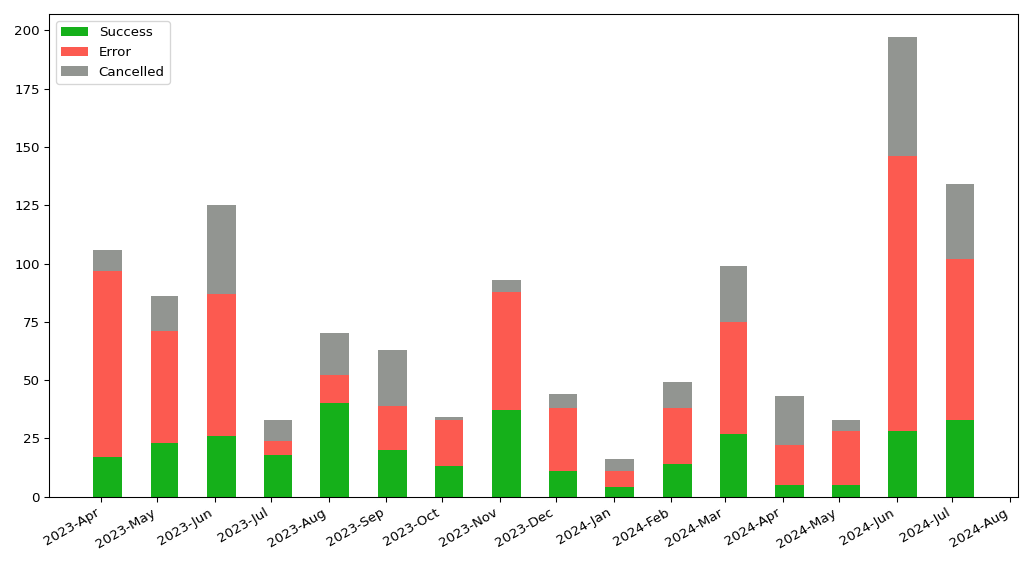

Obiectivul final al acestui proiect a fost atingerea nivelului de maturitate TLR6 a controlerului ce implementează tehnica de verificare adaptiva bazată pe IA. Aceasta a presupus atingerea unei scalabilități ridicate de utilizare pentru o gamă largă de complexitate de circuite caracterizată de un număr mare de condiții de operare și parametri de proces care să poată fi abordată de algoritmul dezvoltat. Figura de mai sus prezintă numărul lunar de experimente efectuate cu unealta de verificare adaptivă pe durata proiectului. Imediat după ce a fost pusă la dispoziția inginerilor de verificare, în martie-aprilie 2023, au fost începute multe experimente, iar numărul mare de erori a fost cauzat de atât de procesul de învățare cât și de problemele inițiale ale uneltei. Pe măsură ce unealta a fost îmbunătățită, procentul de erori și anulări premature ale experimentelor a scăzut. Creșterile ocazionale ale numărului de experimente se datorează noilor utilizatori care încearcă unealta, iar colegii noi trec prin procesul de învățare și generează un procent mare de experimente eronate.

Rezultatele au fost publicate în articole științifice la conferințe și în reviste de profil: